JETIR.ORG

ISSN: 2349-5162 | ESTD Year : 2014 | Monthly Issue

# JOURNAL OF EMERGING TECHNOLOGIES AND INNOVATIVE RESEARCH (JETIR)

An International Scholarly Open Access, Peer-reviewed, Refereed Journal

# A Efficient Approximate Vedic Multiplier: Design, Analysis, and Application in Image

<sup>1</sup>Sruthi Kolaneni, <sup>2</sup>Hemalatha Koppolu, <sup>3</sup>Jeevitha Minchala, <sup>4</sup>Harika Pamujula, <sup>5</sup>Mrs. A.Vidhyullatha

<sup>1</sup>UGScholar, <sup>2</sup>UGScholar, <sup>3</sup>UGScholar, <sup>4</sup>UGScholar, <sup>5</sup>Assistant Professor <sup>1 2345</sup>Department of Electronics and Communication Engineering (ECE), <sup>12345</sup>Narayana Engineering College, Nellore, India

Abstract: Approximate computing has become a widely recognized method for designing energy efficient arithmetic architectures in the context of error-tolerant applications. This paper presents the design and analysis of a 4-bit approximate Vedic multiplier (AVMT) using the Urdhva Tiryagbhyam method. This Vedic approach, involving vertical and crosswise steps, outperforms traditional multiplication in terms of efficiency. An approximate 2-bit multiplier (AVM2) is designed, and an AVMT is proposed using AVM2. The proposed architecture has better propagation delay and less area utilization compared to other conventional multipliers. AVMT has an 11% reduction in area consumption and a 12% increase in processing speed compared to the exact Vedic multiplier. To assess its practicality in real-world scenarios, the proposed multiplier is integrated into an image-blending application. The results indicate that the system achieves a Structural Similarity Index (SSIM) average value of 0.91, which proves to be suitable for error-resilient image processing applications.

Index Terms - Vedic Multiplier, Approximate Computing, Image\_Blending.

#### I. INTRODUCTION

In the realm of modern computing, there is an incessant demand for high-speed and energy-efficient arithmetic operations to support an array of applications, ranging from signal processing to image manipulation. Multipliers, being fundamental components in digital circuits, play a critical role in executing complex multiplication operations, forming the backbone of numerous computational tasks. Traditional multipliers are designed for precise and accurate computations, but they often come at the expense of increased hardware complexity, power, and processing time. As the focus shifts towards optimizing these factors to meet the demands of contemporary computing systems, researchers have explored alternative methodologies that embrace the concept of approximate computing. Approximate computing offers a unique trade-off between computational accuracy and efficiency [1]. It allows for the relaxation of strict precision requirements, thereby Mathematics to perform multiplication operations efficiently. By leveraging techniques like Nikhilam Sutra (specifically UrdhvaTiryagbhyam) and Ekadhikena Purvena, the Vedic multiplier reduces the number of required operations, leading to minimized hardware resources and improved computational speed compared to conventional multipliers

This paper deals with the design of approximate Vedic multiplier using hardware enabling the design of specialized hardware architectures that prioritize speed and reduced hardware utilization [2-3]. Numerous methods for multiplication have been devised to enhance the efficiency of the multiplier, addressing both algorithmic and structural aspects. These methods address the minimization of partial products and their subsequent addition, yet the fundamental principle of multiplication remains consistent across all scenarios. One unique approach is the "VEDIC" (Vedic Mathematics) multiplier, which draws inspiration from ancient Indian mathematical techniques. The Vedic multiplier employs a novel algorithm that exploits the principles of Vedic reduction approximation technique to make it energy-efficient for error-tolerant application. A 4-bit approximate multiplier (AVMT) is proposed with help of 2-bit approximate multiplier (AVM2). AVMT has better electrical hardware performance compared other conventional multipliers. An imageblending application is employed to assess the

effectiveness of the proposed AVMT. The remainder of this paper is organized as follows: Section II delves into the methodology and design principles behind the proposed AVMT. Section III presents a thorough evaluation of the multiplier's performance, including comparisons with conventional multipliers. In Section IV, we detail the integration of the proposed multiplier into an image blending application, showcasing its efficacy and suitability for realworld image processing tasks. Finally, Section V concludes the paper.

#### II. PROPOSED APPROXIMATE VEDIC MULTIPLIER

In this section, the Urdhva-Tiryakbhyam sutra based, an AVM2 is designed with the help of an approximate adder. Finally, AVMT is proposed.

A. Urdhva-Tiryakbhyam

AVM2is designed using Urdhva-Tiryakbhyam vedic mathematics sutra and the multiplication operation is shown in Fig.1.

Fig. 1. Vedic Multiplication

The term "Urdhva

Tiryakbhyam" can be translated as "Vertically and crosswise" in English. This method is a key approach employed in Vedic Mathematics for achieving speedy and effective multiplication [5-7]. Consider the multiplicand and multiplier to be two-bit binary values,  $a_1a_0$ , and  $b_1b_0$ , respectively. In this method, the multiplication process starts by vertically multiplying the least significant bits of two numbers  $(a_0, b_0)$ , namely the multiplicand and the multiplier and the result is  $p_0$ . Subsequently, a crosswise multiplication occurs between the  $a_0$  and  $b_1$ . The result of this multiplication is added to the product obtained from multiplying the  $b_0$  and  $a_1$ . This combined result provides the second bit  $(p_1)$  of the final product along with a carry bit  $(c_1)$ . Continuing the process, the  $a_1$  and  $b_1$  are multiplied vertically. This operation yields the third bit  $(p_2)$  of the final product, accompanied by another carry bit  $(c_2)$  that is fourth bit  $(p_3)$  of the final product [8-11].

# B. Design 2×2 Approximate Vedic Multiplier

Two approximate half adders and four partial product generators are used to design AVM2 that is shown in Fig.2. Final results are four bits and these are  $p_3p_2p_1p_0$ .

Fig. 2. Block Diagram of AVM2

The exact and approximate half-adder truth table is shown in Table.1. In exact half-adder sum is calculated by XOR of A and B. This XOR logic is approximated by the OR gate therefore an error of -1 is produced for input A=1 and B=1 with probability 1/9. The logical expression of an approximate half-adder is defined by equations 1 and 2.

$$S_{app} = A + B$$

(1)

$C_{app} = A.B$  (2)

This AVM2 is useful for the design of energy efficient architecture at a cost of tolerable error. The 2-bit approximate multiplier design uses an approximate half adder, to sum up partial products that make it energy efficient.

# TABLE I. HALF ADDER AND APPROXIMATE HALF ADDER

| A | В | S=A⊕ B | C=A.B | $S_{app}=A+B$ | C <sub>app</sub> =A.B | Error = |

|---|---|--------|-------|---------------|-----------------------|---------|

|   |   |        |       |               |                       | Exact   |

|   |   |        |       |               |                       | Approx  |

| 0 | 0 | 0      | 0     | 0             | 0                     | 0       |

| 0 | 1 | 1      | 0     | 1             | 0                     | 0       |

| 1 | 0 | 1      | 0     | 1             | 0                     | 0       |

| 1 | 1 | 0      | 1     | 1             | 1                     | -1      |

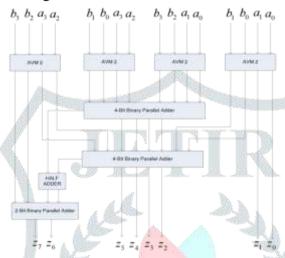

A.Proposed 4-Bit Approximate Vedic Multiplier The architecture of AVMT, is designed by utilizing the principles of the AVM2 in a cascaded manner, is shown in Fig.3. This multiplier operation is described in two stages. In the first stage, the 4-bit numbers are divided into two sets of 2bit numbers, and each set is multiplied using the AVM2

Fig.3. 4-bit Approximate Vedic Multiplier

The results from the first stage are partial products. In the second stage, Binary parallel adders are used to add partial products to obtain the final 8-bit product Z7...Z0. This architecture takes advantage of the UrdhvaTiryakbhyam method's simplicity and effectiveness with approximate computing. It's noteworthy that 8 XOR gates have been replaced with 8 OR gates in this design, and this is due to the use of AVM2.

# III. RESULT ANALYSIS AND DISCUSSION

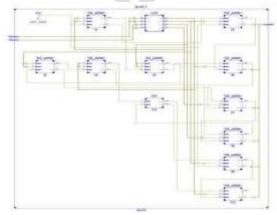

AVMT and other conventional multipliers are coded in Verilog and synthesized using Xilinx ISI 14.7. RTL diagram and functional verification of the proposed AVMT circuit are shown in Fig. 4 and Fig. 5 respectively. The simulation result is shown in Table 2.

Fig.4. RTL diagram of AVMT

Fig.5. Functional verification of AVMT

TABLE. 2. COMPARING AVMT WITH VARIOUS MULTIPLIERS

| meen elem              |     |         |  |  |  |

|------------------------|-----|---------|--|--|--|

| Multipliers            | LUT | Delay   |  |  |  |

| Exact Vedic Multiplier | 54  | 4.12 ns |  |  |  |

| Array Multiplier       | 50  | 3.97ns  |  |  |  |

| AVMT(Proposed)         | 48  | 3.61 ns |  |  |  |

Fig. 6 and 7 illustrate a comparison between AVMT and other multipliers for various parameters. AVMT shows high speed and lower area compared to the exact Vedic multiplier and array multiplier.

Fig.7. Comparison of different multiplier for LUT

The proposed architecture achieves an 11% less area and a 12% increase in processing speed compared to the exact Vedic multiplier. In this design, eight XOR gates have been replaced with 8 OR gates. Compared to OR gates, XOR gates often use more power, take up more area, and can cause slower signal propagation. As a result, at the cost of accuracy, the proposed AVMT circuit is more energy efficient than the others. For accuracy analysis, AVMT is coded into MATLAB and apply all possible inputs. For 256 inputs, only 49 output is erroneous therefore error rate is 18% which is acceptable for error-resilient applications [12].

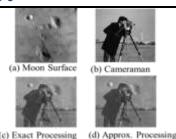

## IV. APPLICATION BLENDING

Image blending is to be used to check the performance of AVMT. SSIM value is used to check the quality of blended images. The range of SSIM is 0-1.[13] Different test images are taken from [14] and multiplied. SSIM values of different blended images are shown in Table.3 and the average SSIM value is 0.91 which is high and acceptable value for error resident systems [15-16]. Some Blended images results are shown in Fig.7.

Fig.7. Blending Images using (c) exact multiplier and (d) approximate multiplier

TABLE.3 SSIM VALUE OF MULTIPLIED IMAGES

| Image Multiplications   | SSIM | Average<br>SSIM |

|-------------------------|------|-----------------|

| Moon Surface -Cameraman | 0.90 | 0.91            |

| Gray- Camerman          | 0.93 |                 |

| Car- Cameraman          | 0.91 |                 |

| Moon Surface-Clock      | 0.88 |                 |

## V. CONCLUSION

In conclusion, this research has demonstrated the potential of approximate computing, specifically in the context of a 4-bit approximate Vedic multiplier, as a viable solution for energy efficient computing. By striking a careful balance between computational accuracy and performance gains, the proposed AVMT showcases notable advantages over conventional multipliers. AVMT has an 11% reduction in area and a 12% increase in processing speed compared to the exact Vedic multiplier. Moreover, the use of AVMT in image blending applications highlights its practicality in real-world scenarios. The obtained SSIM value of 0.91 attests to the suitability of the proposed multiplier for demanding image processing tasks, proving that the obtained AVMT system is suitable for error flexible applications.

# REFERENCES

- [1] CHIPPA, VINAY K., ET AL. "ANALYSIS AND CHARACTERIZATION OF INHERENT APPLICATION RESILIENCE FOR APPROXIMATE COMPUTING." PROCEEDINGS OF THE 50TH ANNUAL DESIGN AUTOMATION CONFERENCE. 2013.

- [2] A. G. M. STROLLO, E. NAPOLI, D. DE CARO, N. PETRA AND G. D. MEO, "COMPARISON EXTENSION OF APPROXIMATE 4-2 COMPRESSORS FOR LOW-POWER APPROXIMATE MULTIPLIERS," IN IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: **REGULAR** PAPERS, VOL. 67. NO. 9. PP. 30213034, SEPT. 2020, DOI: 10.1109/TCSI.2020.2988353.

- [3] GUPTA, VAIBHAV, ET AL. "LOW-POWER DIGITAL SIGNAL PROCESSING USING APPROXIMATE ADDERS." IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS 32.1 (2012): 124-137.

- [4] TIRTHA, SWAMI BHARATI KRISHNA, AND VASUDEVA SHARANA AGRAWALA. VEDIC MATHEMATICS. VOL. 10. MOTILAL BANARSIDASS PUBL., 1992.

- [5] H. D. TIWARI, G. GANKHUYAG, CHAN MO KIM AND YONG BEOM CHO, "MULTIPLIER DESIGN BASED ON ANCIENT INDIAN VEDIC MATHEMATICS," 2008 INTERNATIONAL SOC DESIGN CONFERENCE, BUSAN, KOREA (SOUTH), 2008, PP. II-65-II-68, DOI: 10.1109/SOCDC.2008.4815685.

- P. SAHA, A. BANERJEE, P. BHATTACHARYYA AND A. DANDAPAT, "HIGH SPEED ASIC DESIGN OF COMPLEX MULTIPLIER USING VEDIC MATHEMATICS," IEEE TECHNOLOGY STUDENTS' SYMPOSIUM, KHARAGPUR, INDIA, 2011, PP. 237241, DOI: 10.1109/TECHSYM.2011.5783852.

- [7] K. NEELIMA, C. PADMA, C. NALINI AND M. BALAJI, "FIR FILTER DESIGN USING URDHVA TRIYAGBHYAM BASED ON TRUNCATED WALLACE AND DADDA MULTIPLIER AS BASIC MULTIPLICATION UNIT," 2023 IEEE 12TH INTERNATIONAL CONFERENCE ON COMMUNICATION SYSTEMS AND NETWORK TECHNOLOGIES (CSNT), BHOPAL, INDIA, 2023, PP. 434438, DOI: 10.1109/CSNT57126.2023.10134709.

- [8] SHARMA, VISHIKHA, AND ANIKET KUMAR. "DESIGN, IMPLEMENTATION & PERFORMANCE OF VEDIC MULTIPLIER FOR DIFFERENT BIT LENGTHS." INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN COMPUTER AND COMMUNICATION ENGINEERING 5.4 (2017).

- [9] P. SARITHA, J. VINITHA, S. SRAVYA, V. VIJAY AND E. MAHESH, "4-BIT VEDIC MULTIPLIER WITH 18NM FINFET TECHNOLOGY," 2020 INTERNATIONAL CONFERENCE ON ELECTRONICS AND SUSTAINABLE COMMUNICATION SYSTEMS

- [10] ICESC), COIMBATORE, INDIA, 2020, PP. 1079-1084, DOI: 10.1109/ICESC48915.2020.9155707.

REDDY, CHALIMADUGU DINESH KUMAR, SOMSAGAR RANGANATH REDDY, AND C. ARUL MURUGAN. "IMPLEMENTATION OF MULTIPLIER USING VEDIC MATHEMATICS." MATERIALS TODAY: PROCEEDINGS 65

- [11] PUSHPANGADAN, RAMESH, ET AL. "HIGH SPEED VEDIC MULTIPLIER FOR DIGITAL SIGNAL PROCESSORS." IETE JOURNAL OF RESEARCH 55.6 (2009): 282-286.

- [12] EJTAHED, SEYED AMIR HOSSEIN, AND SOMAYEH TIMARCHI. "EFFICIENT APPROXIMATE MULTIPLIER BASED ON A NEW 1-GATE APPROXIMATE COMPRESSOR." CIRCUITS, SYSTEMS, AND SIGNAL PROCESSING (2022): 1-20.

- [13] ZHOU WANG, A. C. BOVIK, H. R. SHEIKH AND E. P. SIMONCELLI, "IMAGE QUALITY ASSESSMENT: FROM ERROR VISIBILITY TO STRUCTURAL SIMILARITY," IN IEEE TRANSACTIONS ON IMAGE PROCESSING, VOL. 13, NO. 4, PP. 600-612, APRIL 2004, DOI: 10.1109/tip.2003.819861.

- [14] SIPI.USC.EDU. SIPI IMAGE DATABASE (2016). HTTP://SIPI.USC.EDU/DATABASE

- [15] AHMADINEJAD, MOHAMMAD, MOHAMMADHOSSEIN MOAIYERI, FARNAZ SABETZADEH. "ENERGY AND AREA EFFICIENT IMPRECISE COMPRESSORS FOR APPROXIMATE MULTIPLICATION AT NANOSCALE." AEU-INTERNATIONAL JOURNAL OF ELECTRONICS and COMMUNICATIONS 110 (2019): 152859.

- [16] L SAYADI, S. TIMARCHI AND A. SHEIKH-AKBARI, "TWO EFFICIENT APPROXIMATE UNSIGNED MULTIPLIERS BY DEVELOPING NEW CONFIGURATION FOR APPROXIMATE 4:2 COMPRESSORS," IN IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: REGULAR PAPERS, VOL. 70, NO. 4, PP. 1649-1659, APRIL 2023, DOI: 10.1109/TCSI.20.